RZA3UL TES Guiliani Getting Started Guide: Difference between revisions

No edit summary |

|||

| (4 intermediate revisions by the same user not shown) | |||

| Line 23: | Line 23: | ||

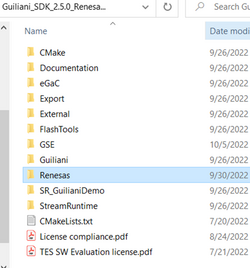

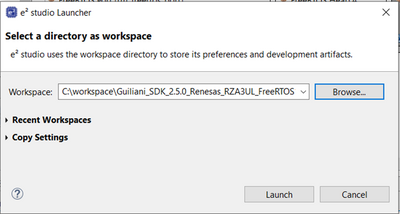

##In the IDE workspace dialog select the Renesas subdirectory in the extracted folder | ##In the IDE workspace dialog select the Renesas subdirectory in the extracted folder | ||

###Example : C:\workspace\Guiliani_SDK_2.5.0_Renesas_RZA3UL_FreeRTOS10_eGML\'''Renesas''' | ###Example : C:\workspace\Guiliani_SDK_2.5.0_Renesas_RZA3UL_FreeRTOS10_eGML\'''Renesas''' | ||

{| | |||

[[File:image 2022-11-02 155357893.png|268x268px]]<li value="3"> | |- | ||

| colspan="3" style="text-align:left" | '''Select Workspace''' | |||

|- | |||

|[[File:image 2022-11-02 155357893.png|268x268px]]<li value="3"> | |||

|[[File:image 2022-11-02 160723018.png|400x400px]] | |||

|} | |||

#<li value="3">The Project Explorer in the IDE should be empty | #<li value="3">The Project Explorer in the IDE should be empty | ||

#Import the TES Projects into the IDE | #Import the TES Projects into the IDE | ||

| Line 59: | Line 64: | ||

= Display Configuration = | = Display Configuration = | ||

The Display Configuration by default are for a 1080p monitor, however the GUI demo is a Wide VGA demo. When displayed on a PC monitor the resulting image is located in the upper left side of the monitor. This section describes how to configure the RZA3UL Display Unit (DU) for a Wide VGA LCD Display. | |||

=== Current Tested Displays : === | |||

{| class="wikitable" | |||

|+ | |||

!Supported LCD | |||

!Link | |||

!Resolution | |||

|- | |||

|GeeekPi 5 Inch Capacitive Touch Screen 800x480 HDMI Monitor | |||

|[https://www.amazon.com/dp/B0749D617J?psc=1&ref=ppx_yo2ov_dt_b_product_details&tag=coa_us-20 Amazon] | |||

|800 x 480 | |||

|- | |||

|DEBO LCD 7 HDMI Entwicklerboards | |||

|[https://www.reichelt.de/de/de/entwicklerboards-display-lcd-touch-7-hdmi-gt811-debo-lcd-7-hdmi-p202677.html?trstct=pos_0&&r=1 reichelt.de] | |||

|1024 x 600 | |||

|} | |||

=== RZA3UL Display Settings using FSP. === | |||

Step 1) Open the BSP Project FSP Configuration file ( configuration.xml ). | |||

Step 2) Select the FSP Configurator "'''Stack'''" Tab. | |||

Step 3) In the Stacks Configuration Tab in the Threads Window, select "'''g_display0 Display on r_lcdc'''" | |||

Step 4) In the bottom of the IDE there are IDE windows ( console, Problems, Smart Brower, Properties, ... ). Select the Properties window. | |||

NOTE: It the Properties Window is not visible, in the IDE memu select Window -> Show View -> Properties. | |||

Step 5) With the "'''g_display0 Display on r_lcdc'''" selected in the FSP configurator you will see the properties for the DU. | |||

Step 6) Expand the Display property Output -> Timing | |||

Step 7) Make the following property changes. | |||

{| class="wikitable" | |||

|+ | |||

!DU Property | |||

!GeekPI | |||

! | |||

! | |||

|- | |||

|Horizontal Total Size | |||

|1056 | |||

| | |||

| | |||

|- | |||

|Horizontal Active Video Cycles | |||

|800 | |||

| | |||

| | |||

|- | |||

|Horizontal back porch Cycles | |||

|216 | |||

| | |||

| | |||

|- | |||

|Horizontal Sync Signal Cycles | |||

|128 | |||

| | |||

| | |||

|- | |||

|Horizontal Sync Signal Polarity | |||

|High Active | |||

| | |||

| | |||

|- | |||

|Vertical Total Size | |||

|628 | |||

| | |||

| | |||

|- | |||

|Vertical Active Video Cycles | |||

|600 | |||

| | |||

| | |||

|- | |||

|Vertical back porch Cycles | |||

|27 | |||

| | |||

| | |||

|- | |||

|Vertical Sync Signal Cycles | |||

|4 | |||

| | |||

| | |||

|- | |||

|Vertical Sync Signal Polarity | |||

|High Active | |||

| | |||

| | |||

|- | |||

|Data Enable Signal Polarity | |||

|High Active | |||

| | |||

| | |||

|} | |||

=== Display Clock Settings === | |||

These steps require modification of the board level display Driver. | |||

Step 1) Open the RA3UL Smarc Board Display Driver file '''rza3ul_smarc_lcd.c'''. This is located here <BSP Project>/src/rza3ul_smarc/ directory. | |||

Step 2) Scroll down to the function "'''bsp_lcd_init'''". | |||

Step 2.1) Change this code snippet | |||

<pre> | |||

/* PLL5 Pixel Clock */ | |||

R_CPG->CPG_SIPLL5_CLK3 = 0x40000006; | |||

R_CPG->CPG_SIPLL5_CLK4 = 0x004a0000; | |||

R_CPG->CPG_PL5_SDIV = 0x01010202; | |||

R_CPG->CPG_SIPLL5_STBY = 0x00150001; | |||

</pre> | |||

Step 2.2) To this | |||

<pre> | |||

/* 40MHz 800x600 */ | |||

uint32_t reg; | |||

uint32_t fracin = 800; | |||

uint32_t intin = 140; | |||

uint32_t refdiv = 2; | |||

uint32_t posdiv1 = 7; | |||

uint32_t posdiv2 = 6; | |||

R_CPG->CPG_SIPLL5_CLK3_b.FRACIN = fracin; | |||

R_CPG->CPG_SIPLL5_CLK4_b.INTIN = intin; | |||

reg = R_CPG->CPG_SIPLL5_CLK1; | |||

reg &= 0xFFFF0000; | |||

reg |= ( (1 << 24) | (1 << 20) | (1 << 16) | (refdiv << 8) | (posdiv2 << 4) | posdiv1 ); | |||

R_CPG->CPG_SIPLL5_CLK1 = reg; | |||

R_CPG->CPG_PL5_SDIV = 0x01010000; | |||

R_CPG->CPG_SIPLL5_STBY = 0x00150001; | |||

</pre>Step 3) Save file this Clean and build the SR_GuilianiDemo project. NOTE: This will clean and build the BSP project tool. | |||

Step 4) Download the project to the RZA3UL. | |||

Latest revision as of 18:27, 3 November 2022

Getting Started

This section describes how to Compile and download the Tes Guilaini Demos on to the RZA3UL.

NOTE: If the IPL has not been loaded refer to the Loading the IPL.

- Extract the Tes Guiliani archive file (Guiliani_SDK_<version>_Renesas_RZA3UL_FreeRTOS10_eGML.zip) to a working directory. ( i.e. C:\workspace ) The resulting directory will look like this.

└── Guiliani_SDK_2.5.0_Renesas_RZA3UL_FreeRTOS10_eGML

├── CMake

├── Documentation

├── Export

├── External

├── FlashTools

├── GSE

├── Guiliani

├── Renesas

├── SR_GuilianiDemo

├── StreamRuntime

└── eGaC

- Start eclipse IDE

- In the IDE workspace dialog select the Renesas subdirectory in the extracted folder

- Example : C:\workspace\Guiliani_SDK_2.5.0_Renesas_RZA3UL_FreeRTOS10_eGML\Renesas

- In the IDE workspace dialog select the Renesas subdirectory in the extracted folder

| Select Workspace | ||

|

| |

- The Project Explorer in the IDE should be empty

- Import the TES Projects into the IDE

- Right click in the Project Explorer and Select Import

- In the Import Dialog select General -> Existing Projects and Workspaces

- In the Import Projects Dialog press the Browes Button then press the Select Folder Button in the popup dialog. Select only the following projects then click Finish.

- BSP

- SR_GuilianiDemo

- Select the SR_GuilianiDemo Project. Right Click and select build. This build will do the following

- The Build will attempt a clean first. This will cause an error as there is nothing to clean

- Next the Build will first build the BSP Library

- Finally the SR_GuilianiDemo will build with no errors

- The Generated executable and library files

- SR_GuilianiDemo ELF file

- Debug information

- SR_GuilianiDemo.sec

- Binary Code

- rza3ul_smarc_qspi_ipl.srec

- IPL boot loader

- Resources.srec

- This is the GUI Widget Resouce file. This is generate the GSE.

- SR_GuilianiDemo ELF file

- Download ( J-Link)

- This section refers the Debug Configuration “Renesas GDB Hardware Debug”.

- Connect power to the USBC connector

- Connect the J-Link to the Smarc Module. Use the dongle that is provided.

- Press and hold the red power button till the power leds are on.

- In the menu select Run -> Debug Configurations

- In the Debug Configuration Dialog select Renesas GDB Hardware Debug then SR_GuilianiDemo Debug.

- NOTE: If Main Tab has a red dot this indicates the Project with the Debug Configuration was not compiled. Return to step 5.

- A Segger Dialog window will show the progress of the download.

- This section refers the Debug Configuration “Renesas GDB Hardware Debug”.

Install the IPL

TBD

Display Configuration

The Display Configuration by default are for a 1080p monitor, however the GUI demo is a Wide VGA demo. When displayed on a PC monitor the resulting image is located in the upper left side of the monitor. This section describes how to configure the RZA3UL Display Unit (DU) for a Wide VGA LCD Display.

Current Tested Displays :

| Supported LCD | Link | Resolution |

|---|---|---|

| GeeekPi 5 Inch Capacitive Touch Screen 800x480 HDMI Monitor | Amazon | 800 x 480 |

| DEBO LCD 7 HDMI Entwicklerboards | reichelt.de | 1024 x 600 |

RZA3UL Display Settings using FSP.

Step 1) Open the BSP Project FSP Configuration file ( configuration.xml ).

Step 2) Select the FSP Configurator "Stack" Tab.

Step 3) In the Stacks Configuration Tab in the Threads Window, select "g_display0 Display on r_lcdc"

Step 4) In the bottom of the IDE there are IDE windows ( console, Problems, Smart Brower, Properties, ... ). Select the Properties window.

NOTE: It the Properties Window is not visible, in the IDE memu select Window -> Show View -> Properties.

Step 5) With the "g_display0 Display on r_lcdc" selected in the FSP configurator you will see the properties for the DU.

Step 6) Expand the Display property Output -> Timing

Step 7) Make the following property changes.

| DU Property | GeekPI | ||

|---|---|---|---|

| Horizontal Total Size | 1056 | ||

| Horizontal Active Video Cycles | 800 | ||

| Horizontal back porch Cycles | 216 | ||

| Horizontal Sync Signal Cycles | 128 | ||

| Horizontal Sync Signal Polarity | High Active | ||

| Vertical Total Size | 628 | ||

| Vertical Active Video Cycles | 600 | ||

| Vertical back porch Cycles | 27 | ||

| Vertical Sync Signal Cycles | 4 | ||

| Vertical Sync Signal Polarity | High Active | ||

| Data Enable Signal Polarity | High Active |

Display Clock Settings

These steps require modification of the board level display Driver.

Step 1) Open the RA3UL Smarc Board Display Driver file rza3ul_smarc_lcd.c. This is located here <BSP Project>/src/rza3ul_smarc/ directory.

Step 2) Scroll down to the function "bsp_lcd_init".

Step 2.1) Change this code snippet

/* PLL5 Pixel Clock */

R_CPG->CPG_SIPLL5_CLK3 = 0x40000006;

R_CPG->CPG_SIPLL5_CLK4 = 0x004a0000;

R_CPG->CPG_PL5_SDIV = 0x01010202;

R_CPG->CPG_SIPLL5_STBY = 0x00150001;

Step 2.2) To this

/* 40MHz 800x600 */

uint32_t reg;

uint32_t fracin = 800;

uint32_t intin = 140;

uint32_t refdiv = 2;

uint32_t posdiv1 = 7;

uint32_t posdiv2 = 6;

R_CPG->CPG_SIPLL5_CLK3_b.FRACIN = fracin;

R_CPG->CPG_SIPLL5_CLK4_b.INTIN = intin;

reg = R_CPG->CPG_SIPLL5_CLK1;

reg &= 0xFFFF0000;

reg |= ( (1 << 24) | (1 << 20) | (1 << 16) | (refdiv << 8) | (posdiv2 << 4) | posdiv1 );

R_CPG->CPG_SIPLL5_CLK1 = reg;

R_CPG->CPG_PL5_SDIV = 0x01010000;

R_CPG->CPG_SIPLL5_STBY = 0x00150001;

Step 3) Save file this Clean and build the SR_GuilianiDemo project. NOTE: This will clean and build the BSP project tool.

Step 4) Download the project to the RZA3UL.