RZA1 FAQ: Difference between revisions

No edit summary |

No edit summary |

||

| Line 26: | Line 26: | ||

While the LVDS is supported in all the RZA1 Drivers the parallel TFT is used for demos. A simple LVDS and parallel demos is available '''here.''' The demos includes the full FreeRTOS SDK for the RZA1H and RZA1M. The demo shows a color black ground that switches between 8 colors. This demo is recommended to verify that the hardware is working, the the VDC Display driver graphics layer is configured correctly, and the display driver control signals (TCON) are correct. Below shows where the configurations are located in the project. | While the LVDS is supported in all the RZA1 Drivers the parallel TFT is used for demos. A simple LVDS and parallel demos is available '''here.''' The demos includes the full FreeRTOS SDK for the RZA1H and RZA1M. The demo shows a color black ground that switches between 8 colors. This demo is recommended to verify that the hardware is working, the the VDC Display driver graphics layer is configured correctly, and the display driver control signals (TCON) are correct. Below shows where the configurations are located in the project. | ||

===== '''LVDS''' ===== | ===== '''Enable LVDS''' ===== | ||

The below code snippets show where to enable the LVDS. Simple set the preprocessor define LVDS = 1; | The below code snippets show where to enable the LVDS. Simple set the preprocessor define LVDS = 1; | ||

File: \src\renesas\application\graphics\inc\lcd__panel.h | * File: \src\renesas\application\graphics\inc\lcd__panel.h | ||

<pre> | <pre> | ||

#if ( TARGET_BOARD == TARGET_BOARD_RSK ) | #if ( TARGET_BOARD == TARGET_BOARD_RSK ) | ||

| Line 43: | Line 41: | ||

#endif | #endif | ||

</pre> | </pre> | ||

File: src\renesas\application\graphics\vdc_portsetting.c | |||

* File: src\renesas\application\graphics\vdc_portsetting.c | |||

<pre> | <pre> | ||

#if (TARGET_BOARD == TARGET_BOARD_RSK) | #if (TARGET_BOARD == TARGET_BOARD_RSK) | ||

| Line 60: | Line 59: | ||

</pre> | </pre> | ||

===== '''LVDS Clock and Graphic Settings''' ===== | |||

The clock and display settings for the LVDS are located here. | The clock and display settings for the LVDS are located here. | ||

\src\renesas\application\graphics\inc\lcd\rsk_lvds_ch0.h | * \src\renesas\application\graphics\inc\lcd\rsk_lvds_ch0.h | ||

* \src\renesas\application\graphics\inc\lcd\rsk_lvds_clk.h | |||

\src\renesas\application\graphics\inc\lcd\rsk_lvds_clk.h | |||

Revision as of 20:52, 14 December 2021

RZA1 LVDS

Supported Devices

- RZA1H

- RZA1M

Supported RZA1 Boards

- RZA1H Display-it Kit ( RSK )

- RZA1H MBED GR-Peach

RZA1H Display-it Kit ( RSK ) Modifications

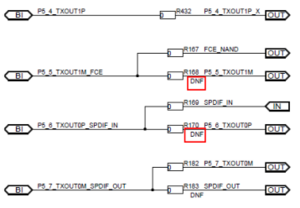

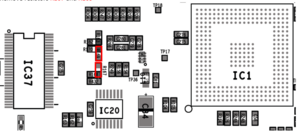

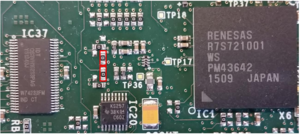

For the RZ/A1 RSK Board, some resistor changes are needed in order to route all the LVDS signals to the CN17 connector. On the RSK board, the defaults 0-Ohm resistor populations for P5_5 is for RAW NAND flash, and P5_7 is for SPDIF_OUT (S/PDIF digital audio interface).

- Remove the resisters R167 and R169.

- Place the removed resisters to location of R170 and R168.

RZA1 LVDS Demo Project

While the LVDS is supported in all the RZA1 Drivers the parallel TFT is used for demos. A simple LVDS and parallel demos is available here. The demos includes the full FreeRTOS SDK for the RZA1H and RZA1M. The demo shows a color black ground that switches between 8 colors. This demo is recommended to verify that the hardware is working, the the VDC Display driver graphics layer is configured correctly, and the display driver control signals (TCON) are correct. Below shows where the configurations are located in the project.

Enable LVDS

The below code snippets show where to enable the LVDS. Simple set the preprocessor define LVDS = 1;

- File: \src\renesas\application\graphics\inc\lcd__panel.h

#if ( TARGET_BOARD == TARGET_BOARD_RSK ) #define LVDS 1 /* 0 or 1 */ #if (LVDS==0) #include "lcd/rsk_tft_clk.h" /* user define */ #include "lcd/rsk_tft_ch0.h" /* QE for Video Display Controller 5 output header file */ #elif (LVDS==1) #include "lcd/rsk_lvds_clk.h" /* user define */ #include "lcd/rsk_lvds_ch0.h" /* QE for Video Display Controller 5 output header file */ #endif

- File: src\renesas\application\graphics\vdc_portsetting.c

#if (TARGET_BOARD == TARGET_BOARD_RSK)

#define LVDS 1 /* 0 or 1 */

#if (LVDS == 0)

/* RSK TFT (RGB888)

Panel clock : LCD0_CLK ... P11_15, 5th alternative function

HSYNC : LCD0_TCON2 ... P11_12, 5th alternative function

VSYNC : LCD0_TCON3 ... P11_11, 5th alternative function

DE : LCD0_TCON4 ... P11_10, 5th alternative function

LCD0_DATA

R[7:0] : LCD0_DATA[23:16] ... P10_0 ~ P10_7, 5th alternative function

G[7:0] : LCD0_DATA[15:8] ... P10_8 ~ P10_15, 5th alternative function

B[7:0] : LCD0_DATA[7:0] ... P11_0 ~ P11_7, 5th alternative function

*/

LVDS Clock and Graphic Settings

The clock and display settings for the LVDS are located here.

- \src\renesas\application\graphics\inc\lcd\rsk_lvds_ch0.h

- \src\renesas\application\graphics\inc\lcd\rsk_lvds_clk.h